Hierarchical LVS is now a reality in Revolution EDA

28/04/2026 — Revolution EDA can now perform hierarchical LVS rivalling legacy offerings

Huissen, the Netherlands - Revolution EDA is excited to announce a major milestone: comprehensive hierarchical Layout vs Schematic (LVS) verification is now available, bringing professional-grade design validation to the open-source electronic design automation community.

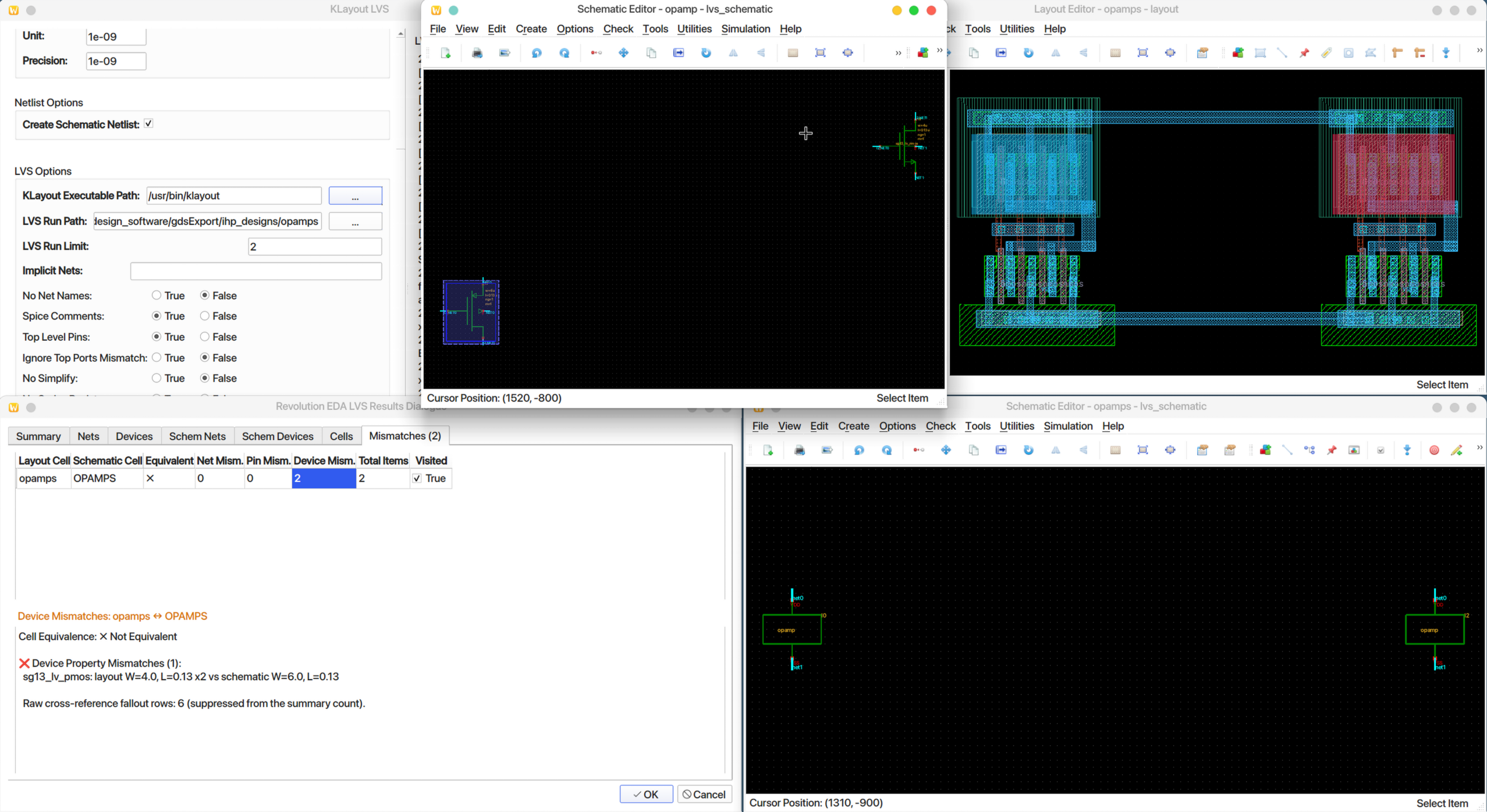

First example of LVS functionality is offered for IHP SG13G2 technology using IHP provided rule-decks, KLayout is used in headless mode to run IHP rule-decks. Revolution EDA’s seamless integration from schematic to layout provides an hitherto unmatched functionality in a shared-source electronic design automation environment.

What is LVS Verification?

Layout vs Schematic (LVS) verification is a critical step in integrated circuit design that ensures the physical layout of a chip matches exactly with its schematic representation. This verification process catches design errors before they reach the fabrication stage, preventing costly manufacturing failures and ensuring design integrity.

Revolution EDA’s LVS Solution

The new hierarchical LVS tool in Revolution EDA offers:

Core Capabilities

- True Hierarchical Processing: Maintains design hierarchy throughout verification, enabling efficient handling of complex designs

- Intelligent Netlist Extraction: Automatically extracts precise netlists from hierarchical layouts with support for multiple levels of abstraction

- Device-Level Verification: Recognizes and verifies transistors, resistors, capacitors, and other devices with support for multiple technology nodes

- Pin and Port Matching: Validates all pins, ports, and connections between layout and schematic views

- Detailed Violation Reporting: Provides comprehensive reports with visual references, pinpointing exact mismatches

Seamless Integration

The LVS tool integrates perfectly with Revolution EDA’s existing layout and schematic editors:

- Run verification directly from the layout editor interface

- Navigate between layout and schematic to investigate and fix violations

- Apply corrections and re-verify in a streamlined workflow

Open Source, No Licensing Barriers

Like all Revolution EDA tools, hierarchical LVS is completely free under the Mozilla Public License v2.0 with Commons Clause. There are no licensing fees, node counts, or subscription requirements—making advanced verification accessible to everyone from hobbyists to professional engineering teams.

Roadmap for Future Enhancements

The development team is already working on additional features:

- RC Extraction: Parasitic resistance and capacitance extraction for accurate timing analysis

- Cross-Probe Navigation: Direct linking between layout violations and schematic elements

- Additional PDK Support: Expanded compatibility with more open and commercial technology nodes

- AI-Assisted Debugging: Machine learning-powered insights for faster violation resolution